总线

基本概念

总线 是一组电子导线或信号线,它们允许不同的硬件设备(如 CPU、内存、输入/输出 设备等)之间进行数据传输和通信。总线是计算机内部和外部设备之间的信息传递通道。

总线分类

功能

- 核内总线 :在处理器核内部各元件之间连线的总线称为 核内总线 ,可连接核内各寄存器、ALU、指令部件等

- 系统总线 :指连接 CPU、主存和 I/O 接口等主要部件的总线,通常所说的总线是指这类在系统主要模块之间互连的总线。下面要介绍的也是这种 系统总线 。

- 通信总线 :计算机系统之间或计算机系统与其他系统(远程通信设备、测试设备)之间进行通信的总线,又称 外部总线。

数据传送方式

总线 的数据传输方式包含 串行 和 并行 两种:

- 串行总线 :只含有一条双向数据线或两条单向数据线,数据按位分时传送。适合远距离通信,大多数 通信总线 属于 串行总线

- 并行总线 :含有多条双向数据线,可实现多位同时传送。传输效率高,但相邻数据线之间会相互干扰,适合近距离传输。大多数 系统总线 属于 并行总线

试题中常常考查 哪些总线是串行总线,哪些总线是并行总线 。

这里核心把握一点:现代高速通信几乎都使用串行总线(PCIe、USB、SATA、DisplayPort),而并行总线主要用于内存、老式设备或非常短距离的高速通信。

常见的串行总线 如下表所示:

| 总线类型 | 简介 |

|---|---|

| USB(通用串行总线) | 广泛用于外设连接,如鼠标、键盘、U盘。支持热插拔。 |

| PCI Express (PCIe) | 高速内部总线,连接显卡、SSD 等。点对点串行通信。 |

| SATA(串行ATA) | 硬盘、SSD 与主板间通信。取代并行ATA(PATA)。 |

| Thunderbolt | 基于 PCIe 和 DisplayPort 的高速接口,可传输视频、数据。 |

| DisplayPort、HDMI、DVI | 显示器接口,虽然传视频数据,但本质上是高速串行通信。 |

常见的并行总线 如下表所示:

| 总线类型 | 简介 |

|---|---|

| PCI(老式) | 并行总线,早期主板与扩展卡连接标准,已被 PCIe 取代。 |

| ISA(工业标准架构) | 更早的并行总线,已淘汰。 |

| IDE / PATA(并行ATA) | 老式硬盘连接方式,已被 SATA 取代。 |

| 内存总线(如 DDR) | 尽管速率非常高,但 DRAM 模块仍通过并行数据线传输数据(如 DDR4 有 64 数据线)。 |

时序控制方式

- 同步总线 :采用公共的时钟信号进行定时,挂接在总线上的所有设备都从时钟线上获得定时信号

- 总线 定时以 最慢设备 所用时间为标准,因此适合于存取时间相差不大的多个功能部件之间的通信

- 由于时钟偏移问题,导致 同步总线 不能过长,否则会降低 总线 传输效率

- 同步总线 常采用 并行传输,即总线的数据条数为 8、16、32 或 64 位等

- 异步总线 :总线上连接的各部件或设备没有统一的时钟,而是依靠各自内部的定时操作,通过 信号握手 的方式来进行规定的总线操作,从而完成部件或设备之间的数据传输

- 由于 同步并行总线 使用快速且长的传输线时,会导致传送到另一端的波形发生变形,从而使得(并行传输的)所有位中最快和最慢的位信号之间的时间差较大,因此现在更多使用 异步串行方式 进行传输:串行–传输速率可更快 + 不会影响到其他位

总线架构方式

总线 架构方式可以分成 单总线、多总线 以及 分层结构 三种。

单总线结构

- 单总线结构 中,所有处理器、主存储器和 I/O 设备 共用一条总线进行通信 。

- 优点是结构简单、实现成本低,适用于设备数量少、通信量低的系统。

- 缺点是所有设备必须轮流访问总线,存在通信冲突和带宽瓶颈,性能扩展性差。

多总线结构

- 多总线结构 在 单总线 的基础上进行拓展,引入多条功能分化的总线,例如系统总线、I/O 总线、存储器总线等。

- 常见做法是将 处理器与主存之间的数据传输 放在一条专用总线(如 CPU-主存总线),而 I/O 设备通过桥接芯片连接至另一条总线(如 I/O 总线)。

- 这样可以显著减轻主总线负载,提高系统并发性和吞吐能力。

分层总线结构

现代计算机系统广泛采用 分层总线结构,其核心思想是在 多总线结构 的基础上进一步 细化总线的功能与等级,以更好适应不同设备对带宽和延迟的需求。

核心特点 :

- 将总线按速率和用途分层,如高速、中速、低速总线;

- 各层通过 桥接控制器(如 PCH)进行协调;

- 高速设备尽量绕过中间桥接器,直连 CPU 提高性能。

- 高速设备的连接方式

- 内存总线 :使用 DDR4/DDR5 等内存通道,由集成在 CPU 内部的内存控制器(IMC)控制,实现低延迟高速访问;

- 显卡 :通过 PCIe 高速通道,直接连接到 CPU 的 PCIe 控制器,适用于图形、大数据等吞吐密集型场景;

- 高速存储 (如 NVMe SSD) :通过 PCIe/NVMe 通道连接,可直连 CPU 或走 PCH。

- 低速或通用设备的连接方式

- 低速设备(如 USB、SATA、音频、网卡等)大多连接至 平台控制器集线器(PCH) 或 南桥芯片,再通过 DMI(Direct Media Interface)总线 与 CPU 通信;

- 这些设备不要求极高带宽,通过桥接方式集中管理,可简化主板设计并降低成本。

总线组成

系统总线 通常由一组控制线、一组数据线和一组地址线构成。也有些总线没有单独的地址线,即数据线和地址线 复用。

- 数据总线(Data Bus) :数据总线用于在计算机系统的各个组件之间 传输数据。它通常由多条并行线组成,每条线传输一个数据位(比特)。

- 位数(数据总线条数)与机器字长、存储字长有关,一般是 8 位、16 位、32 位

- 地址总线(Address Bus) :地址总线用于传输 内存地址 或外部设备的地址信息,以确定数据的存储位置或目标设备。

- 地址总线的宽度决定了系统可以寻址的内存或设备的数量。更宽的地址总线通常允许系统寻址更多的内存或设备。

- 控制总线(Control Bus) :控制总线传输 控制信号和命令,用于控制各个硬件组件的操作。这些控制信号包括读/写信号、时钟信号、中断信号、复位信号等。控制总线用于协调数据传输和操作的序列。

总线组成和总线架构的关系 :

- 在 单总线架构 中,所有的通信—包括数据、地址和控制信息—都通过同一个物理总线传输。这意味着数据总线、地址总线和控制总线的功能在一个共享的通道上实现。

- 在 多总线架构 中,数据总线、地址总线和控制总线可能会分别拥有独立的物理通道,或者系统中可能存在专门的总线来处理不同类型的数据流。

总线指标

总线时钟频率时钟频率 指总线所依赖的时钟信号的频率。它表示的是“时钟脉冲”产生的快慢。

时钟频率 单位 为 Hz,常见如 100MHz、133MHz 等。

总线传输周期总线传输周期 指一次完成总线数据传输所需的时间,包括申请、寻址、传输和结束阶段。

一个完整的传输周期可能需要 多个时钟周期。

总线工作频率工作频率 指总线 实际传输数据 的频率。

一般来说,工作频率与时钟频率相同,但有些总线为了提高带宽,会采用 倍频/分频 机制:

- SDR(单倍数据率):每个时钟周期只在一个边沿传输数据,工作频率 = 时钟频率。

- DDR(双倍数据率):在上升沿和下降沿各传输一次,工作频率 = 2 × 时钟频率。

- QDR(四倍数据率):一个周期传四次,工作频率 = 4 × 时钟频率。

更加泛化地说,若总线传输周期 = N 个时钟周期,则总线的工作频率 = 时钟频率 / N。

总线宽度总线宽度 也叫做总线位宽,是总线上 能同时传输的数据位数,通常指的是数据总线的根数,如 32 根称为 32 位总线。

总线带宽总线带宽 指单位时间内总线能传输的最大数据量,通常用 MB/s、GB/s 表示,计算公式为:

$$\text{带宽} = (\text{总线宽度} / 8) \times \text{工作频率}$$

常见总线标准

需要熟练掌握一些会考察的 总线标准 的名称:PCI、SATA、ISA、IDE、USB,并且能够和其他计算机领域的专业名词区分开来:

- PCI :PCI 总线 是一种用于连接内部扩展卡(如显卡、网卡、声卡等)到主板的标准。PCI 总线 存在多个版本,包括 PCI、PCI-X 和 PCI Express(PCIe),它们在带宽、速度和适用范围上有所不同。

- SATA :SATA 是一种用于连接存储设备(如硬盘驱动器和光盘驱动器)到计算机的总线标准。它广泛应用于个人电脑和服务器中。

- ISA :16 位体系结构,只能支持 16 位的 I/O 设备,是已经被淘汰的插槽接口。

- IDE :IDE 是早期计算机中用于连接硬盘驱动器和光盘驱动器的 总线 标准,现在已经被 SATA 所取代。

- USB :USB 是一种通用的总线标准,用于连接各种外部设备(如键盘、鼠标、打印机、存储设备等)到计算机。USB 有多个版本,包括 USB 1.0、USB 2.0、USB 3.0、USB 3.1 和 USB 3.2,它们在传输速度和功能上有所区别。

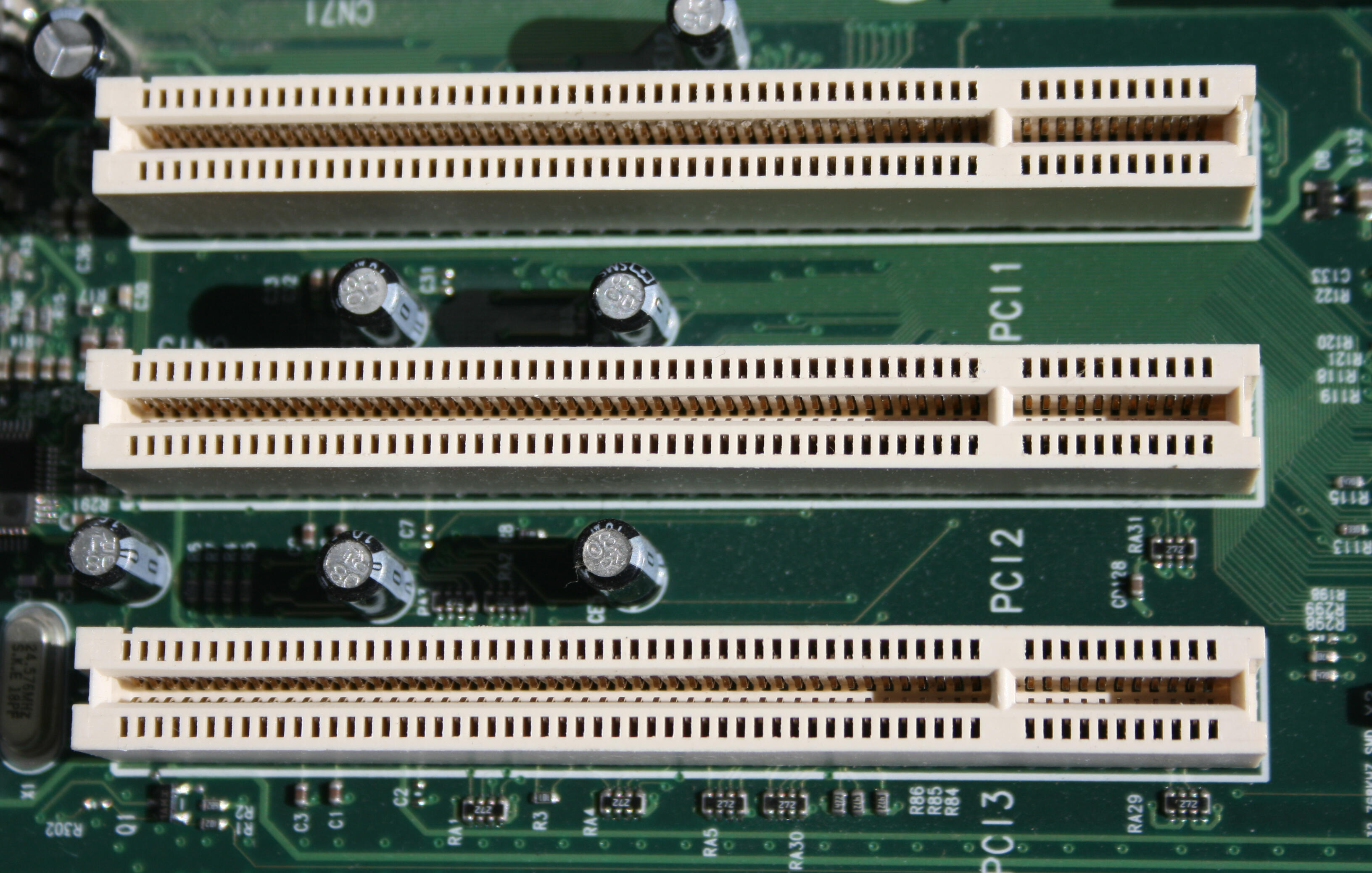

PCI

Peripheral Component Interconnect

长条形插槽,通常为长方形,长度较长,内部有多个金属触点,呈平行排列,用于插入扩展卡。边缘有一缺口,用于固定卡的位置。

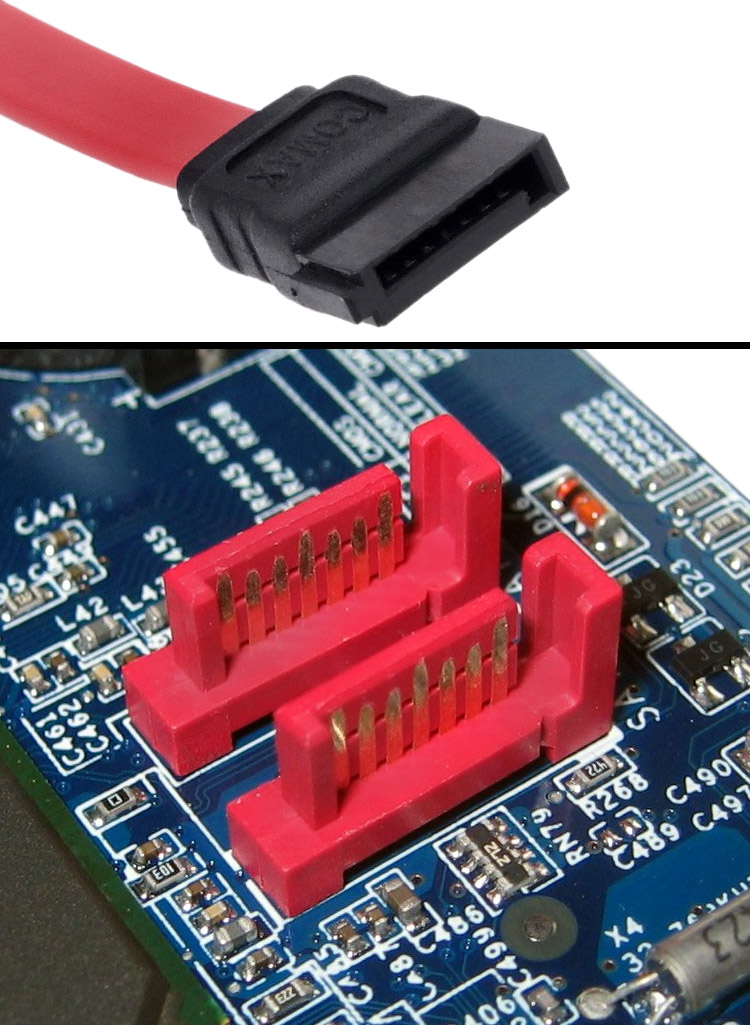

SATA

Serial Advanced Technology Attachment

较小的 L 形连接器,扁平且细长,端口一侧有明显的 L 形弯角,内部有几根细小金属针脚,用于连接存储设备(如硬盘驱动器和光盘驱动器)到计算机。

USB

Universal Serial Bus

矩形接口,较为紧凑,内部有金属触点,常见为USB-A的扁平长方形设计,端口内部有塑料隔板和触点,用于连接各种外设如鼠标、键盘或U盘。

这三个概念是经常被混淆的概念,这里还是多提一嘴。简单来说,接口 是硬件插入的位置,协议 是软件层面用于通信的规则,总线 是硬件之间的数据通路。下表给出一些常见例子来说明:

| 实际例子 | 插槽/接口 | 协议 | 总线 |

|---|---|---|---|

| SATA SSD | SATA 接口 | AHCI 协议 | SATA 总线 |

| M.2 SATA SSD | M.2 插槽 | AHCI 协议 | SATA 总线 |

| M.2 NVMe SSD | M.2 插槽 | NVMe 协议 | PCIe 总线 |

| PCIe 显卡 | PCIe 插槽 | PCIe 协议 | PCIe 总线 |

| USB U盘 | USB-A 接口 | USB 协议(2.0/3.0/3.1 等) | USB 总线 |

需要注意的是,有些名词(比如 SATA、PCIe、USB)是 混合性术语,既可以是 总线,也代表了协议和接口;有些名词(比如 M.2) 仅仅是接口;有些名词(比如 NVMe)仅仅是协议。

总线事务

总线事务 是计算机总线操作的一个 基本单位。一个总线事务通常涉及一系列的操作,这些操作可以是数据的读取或写入。

在一个总线事务中,主设备(发起事务的设备)通过总线控制线对总线进行控制,并发出地址和数据,以及读写信号。从设备(数据被读取或写入的设备)则识别地址,并根据读写信号进行相应的数据交换。

总线事务 包含几个主要阶段:

- 请求(Request) :主设备发出 总线传输请求。

- 仲裁(Arbitration) :如果多个设备同时尝试使用总线,它们必须通过某种仲裁过程来 决定哪个设备有权 控制总线。这通常涉及一个优先级方案,以防止冲突和数据损坏。

- 寻址(Addressing) :主设备将 目标地址 放在总线上,以指定事务的目的地,如特定的内存地址或 I/O 设备。

- 传输(Transfer) :一旦地址被确认,数据传输就会发生。这可以是读操作,也可以是写操作。

- 终止(Termination) :一旦数据成功传输,事务就会结束。终止阶段可能包括从设备发出的确认信号,或者主设备撤销其对总线的控制。

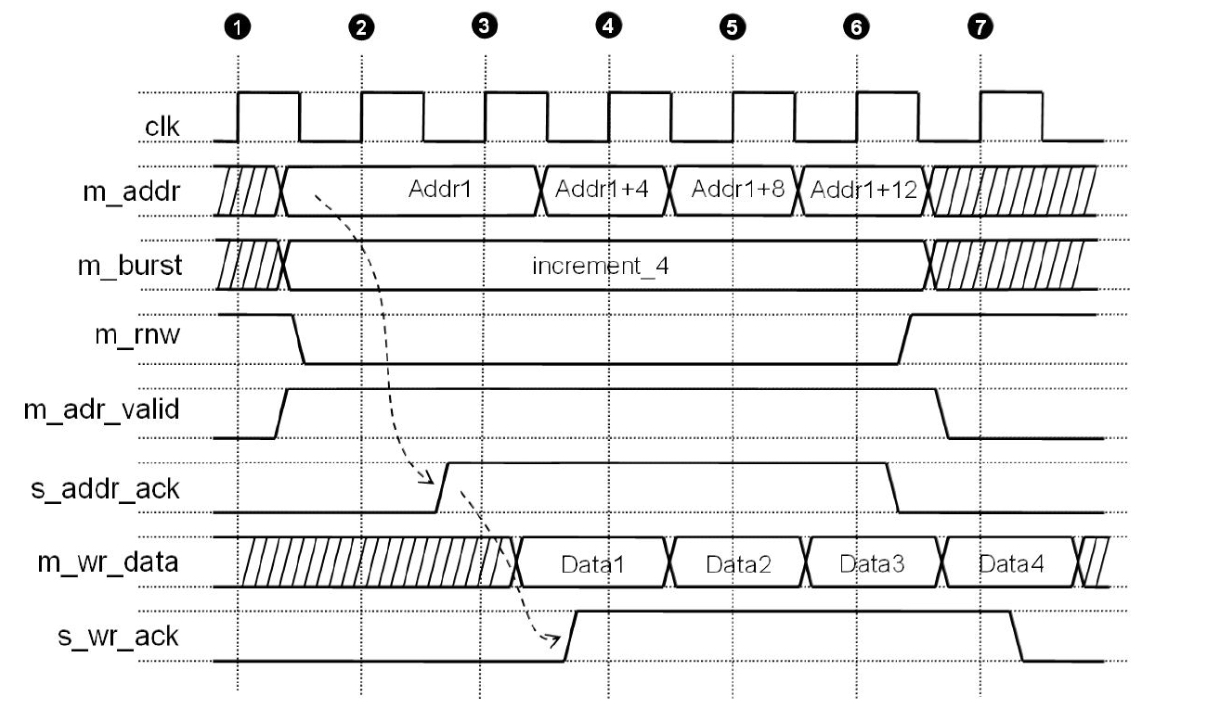

突发总线传输事务

突发(Burst) 总线传输事务 是指在总线通信中,一次性连续传输多个数据单元(通常是字节或字)而无需为每个数据单元单独发起请求或握手的过程。这种传输方式广泛应用于现代计算机体系结构中,以提高数据传输效率和总线利用率。

总线周期

总线周期 是指 CPU 通过 总线 与存储器或 I/O 接口进行一次数据传输所需的时间。

一个 总线周期 通常包含多个时钟周期,这些时钟周期可以被分为四个阶段(四个时钟周期 $T_1, T_2, T_3, T_4$):

- 申请分配阶段:主设备进行请求和仲裁。

- 寻址阶段:主设备用地址信息来指明它想读/写的那个从设备是哪一个。

- 传输阶段:主设备向从设备发出读命令或者写命令。

- 结束阶段:主设备把地址信息、读写命令等从 总线 撤除,让出 总线 的使用权。

总线定时

根据 时钟周期 一节可知,计算机中的设备也许并不使用相同的时钟周期,但是设备间在交换数据的过程中需要时间上配合。

这种时间配合的控制过程就叫做 总线定时,总线定时 包含 同步定时 和 异步定时 两种方式。

同步定时方式

在 同步定时方式 中,数据传输的时钟信号由一个 中央时钟源(通常是主时钟源或总线控制器)生成,并将时钟信号传送到所有参与通信的设备。

这个时钟信号每次都产生一个相等的时间间隔,这个间隔为一个 总线传输周期,主设备和从设备必须在这个限定的时间内完成规定的操作。

- $T_{1}$ 的上升沿到来时,主模块向从模块发送地址

- $T_{2}$ 的上升沿到来时,主模块发送读命令

- $T_{3}$ 的上升沿到来时,从模块提供数据

- $T_{4}$ 的上升沿到来时,主模块撤销读命令,从模块撤销数据

同步通信适用于总线长度较短(出现信息错误的概率小)及总线所接部件的存取时间比较接近的系统。

如果有的从设备速度较慢,就会跟不上总线的节奏,进而拖慢了主设备的速度。

异步定时方式

在 异步定时方式 中,数据传输的时钟信号不是由中央时钟源统一控制,而是由每个设备自己的时钟信号驱动。完全依靠传送双方相互制约的“握手”信号来实现定时控制,通常我们将交换信息的两个设备称为主设备和从设备,主设备发送“请求”,从设备接收到后回复“回答”。

异步定时 根据“请求”和“回答”的类型,可以分为三种类型:

- 不互锁 :主设备持续发送请求一段时间,默认从设备接收到请求。

- 半互锁 :主设备接收到来自从设备的回答后停止发送请求,从设备发送回答一段时间,默认主设备接收到回答。

- 全互锁 :从 半互锁 的基础上,从设备接收到来自于主设备的回答后停止发送回答。